| U.S.N |  |  |  |  |  |

|-------|--|--|--|--|--|

# P.E.S. College of Engineering, Mandya - 571 401

(An Autonomous Institution affiliated to VTU, Belagavi)

## Third Semester, B.E. - Electrical and Electronics Engineering Semester End Examination; Dec - 2017/Jan - 2018 Digital Electronics

Time: 3 hrs Max. Marks: 100

Note: Answer FIVE full questions, selecting ONE full question from each unit.

#### UNIT - I

- 1 a. With the help of circuit diagram, explain the working of,

- i) NAND

- ii) NOR

- iii) X-OR Gate.

- b. Show that  $(A+B)(\overline{AB}) = A \oplus B$  with logic diagram.

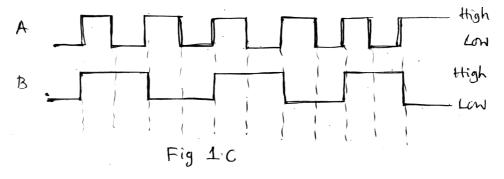

- c. The waveforms A and B shown in Fig. 1.c are applied to a two input NAND gate. Determine the output waveform:

- 2 a. State and prove De Morgan's theorem.

- b. Realize the XOR function using NOR logic only.

- c. With examples, explain the SOP and POS standard forms to express Boolean function.

### **UNIT-II**

- 3 a.  $F(A B C D) = \Sigma m(1, 5, 6, 12, 13, 14) + d(2, 4)$  reduce by K-map and implement using NOR logic.

- b. Distinguish between prime implicants and essential prime implicants.

- c. Outline the basic Quine Mc-Cluskey procedure for simplifying a Boolean expression.

- 4 a. Design Half adder using NOR logic.

- b. What is parallel binary adder? With example, demonstrate the working of binary adder.

- c. With block diagram and truth table, explain the implementation of full subtrator.

#### **UNIT - III**

- 5 a. Design BCD to decimal decoder with use of decoder.

- b. Explain the operation of basic SR Latch with NOR gates.

- c. Convert JK flip-flop to T flip-flop.

8

10

6

4

8

6

6

8

6

6

10

4

6

6

6

| P15EE34 Page |                                                                                           | )<br>'    |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------|-----------|--|--|--|--|

| 6 a.         | Obtain the characteristic equation of :                                                   |           |  |  |  |  |

|              | i) JK flip-flop                                                                           | 8         |  |  |  |  |

|              | ii) Edge triggered D flip-flop.                                                           |           |  |  |  |  |

| b.           | . Implement the 4 to 1 line multiplexer with block diagram and function table.            |           |  |  |  |  |

| c.           | Convert JK flip-flop to D flip-flop.                                                      |           |  |  |  |  |

|              | UNIT - IV                                                                                 |           |  |  |  |  |

| 7 a.         | . Distinguish between synchronous and asynchronous counters.                              |           |  |  |  |  |

| b.           | With a neat timing diagram, explain the working of serial-in-parallel-out shift register. |           |  |  |  |  |

| c.           | Explain the operation of Four-bit synchronous binary counter.                             |           |  |  |  |  |

| 8 a.         | . Explain the Mealy and Moore models of clocked synchronous sequential network.           |           |  |  |  |  |

| b.           | . Write a block diagram of a finite state model and explain.                              |           |  |  |  |  |

| c.           | Define;                                                                                   |           |  |  |  |  |

|              | i) State diagram ii) State tabel                                                          | 4         |  |  |  |  |

|              | iii) Transition tabel iv) Excitation tabel.                                               |           |  |  |  |  |

|              | UNIT - V                                                                                  |           |  |  |  |  |

| 9 a.         | Draw the schematic circuit and explain the operation of R-2R Ladder type DAC.             |           |  |  |  |  |

| b.           | Draw and explain basic block diagram of a 4 bit successive approximation type ADC.        |           |  |  |  |  |

| 10 a.        | Draw and explain the operation of 3 bit Flash type A/D converter.                         |           |  |  |  |  |

| b.           | . List the different types of Logic families circuits and compare them Emitter-coupled de | elay<br>5 |  |  |  |  |

|              | time.                                                                                     |           |  |  |  |  |

| c.           | Outline the characteristics of Emitter-Coupled Logic (ECL).                               |           |  |  |  |  |