*i*)

$$f(x, y, z) = \sum m(0, 2, 4, 5, 7)$$

*ii*)  $f(w, x, y, z) = \sum m(1, 3, 7, 8, 9, 14, 15)$

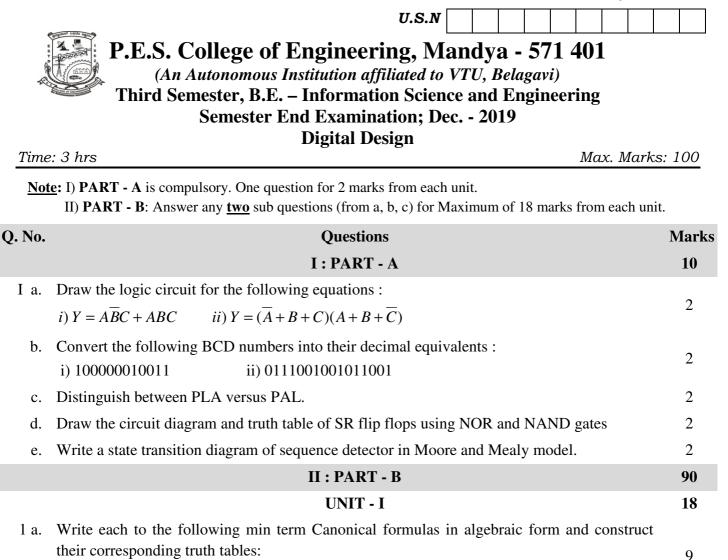

Write a Boolean expression for each of the logic diagram in Fig.1(b) b.

с. Using K-maps determine all the minimal sums and minimal products for each of the following Boolean functions.

i)

$$f(w, x, y, z) = \sum m(0, 1, 6, 7, 8, 14, 15)$$

ii)  $f(w, x, y, z) = \prod M(4, 6, 7, 8, 12, 14)$

iii)  $f(w, x, y, z) = \overline{wxz} + xyz + \overline{wxz} + \overline{xyz}$

Contd...2

9

| P17IS32 Page No 2 |                                                                                                                                                                                                                      |    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                   | UNIT - II                                                                                                                                                                                                            | 18 |

| 2 a.              | Realize the function $f(x, y, z) = \sum m(0, 2, 3, 5)$ using 4:1 line multiplexer.                                                                                                                                   | 9  |

| b.                | Write and explain the parity generator and checker circuits.                                                                                                                                                         | 9  |

| c.                | Explain the construction of 4-bit carry lookahead adder.                                                                                                                                                             | 9  |

|                   | UNIT - III                                                                                                                                                                                                           | 18 |

| 3 a.              | Realize the following Boolean expression using Programming Logic Array (PLA) and Programming Array Logic (PAL) :                                                                                                     |    |

|                   | <i>i</i> ) $f_1(w, x, y, z) = \sum m(2, 4, 5, 10, 12, 13, 14)$                                                                                                                                                       | 9  |

|                   | <i>ii</i> ) $f_2(w, x, y, z) = \sum m(2, 9, 10, 11, 13, 14, 15)$                                                                                                                                                     |    |

| b.                | What is the full scale output voltage of a 6 bit binary ladder of 0 = 0 V and 1 = +10 V of an8-bit ladder? Find the output voltage of a 6-bit binary ladder with the following inputs?i) 101001ii) 111011iii) 110001 | 9  |

| c.                | Explain the Read Only Memory diode circuits.                                                                                                                                                                         | 9  |

|                   | UNIT - IV                                                                                                                                                                                                            | 18 |

| 4 a.              | Give the characteristic equation, excitation table, state diagram of SR flip flop and JK flip flop.                                                                                                                  | 9  |

| b.                | Illustrate how JK flip flops can be converted to SR flip flops?                                                                                                                                                      | 9  |

| c.                | With circuit diagram, explain serial in serial out and parallel in serial out shift registers.                                                                                                                       | 9  |

|                   | UNIT - V                                                                                                                                                                                                             | 18 |

| 5 a.              | Design an asynchronous up down counter.                                                                                                                                                                              | 9  |

|                   |                                                                                                                                                                                                                      |    |

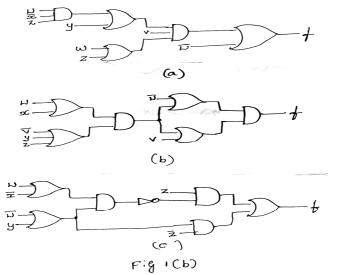

b. Using row elimination method to reduce the state diagram as shown in Fig. 5(b).

9

9

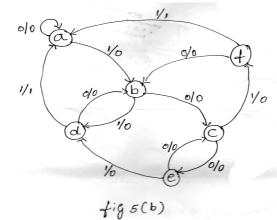

c. i) Analyze the mealy model asynchronous sequential circuit of Fig. 5(c) and show its stable state and corresponding outputs.

ii) Give the state diagram of the circuit as shown in Fig.5(c)

\* \* \*