| P181                                                                                                                                                                                                        | P18IS32 Pag                                                                                                                                                  |       |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

|                                                                                                                                                                                                             | U.S.N                                                                                                                                                        |       |  |

| P.E.S. College of Engineering, Mandya - 571 401<br>(An Autonomous Institution affiliated to VTU, Belagavi)<br>Third Semester, B.E Information Science and Engineering<br>Semester End Examination; Dec 2019 |                                                                                                                                                              |       |  |

|                                                                                                                                                                                                             | Digital DesignTime: 3 hrsMax. Marks: 10                                                                                                                      | 00    |  |

| Note: I                                                                                                                                                                                                     | ) <b>PART - A</b> is compulsory. <b>Two</b> marks for each question.                                                                                         |       |  |

|                                                                                                                                                                                                             | ) <b>PART - B</b> : Answer any <u><b>Two</b></u> sub questions (from a, b, c) for Maximum of <b>18 marks</b> from each unit.                                 |       |  |

| Q. No.                                                                                                                                                                                                      | Questions                                                                                                                                                    | Marks |  |

|                                                                                                                                                                                                             | I:PART - A                                                                                                                                                   | 10    |  |

| I a.                                                                                                                                                                                                        | What is the Boolean function obtained for the following truth table:                                                                                         |       |  |

|                                                                                                                                                                                                             | $\begin{array}{c ccc} x & y & f(x, y) \\ \hline 0 & 0 & 0 \\ \hline 0 & 1 & 0 \\ \hline 1 & 0 & 1 \\ \hline 1 & 1 & 1 \end{array}$                           | 2     |  |

| b.                                                                                                                                                                                                          | Obtain the minimal form from the K-map                                                                                                                       |       |  |

|                                                                                                                                                                                                             | a <u>bc</u><br>a <u>1 X X 1</u><br><u>1 X</u>                                                                                                                | 2     |  |

| c.                                                                                                                                                                                                          | Give the excitation table of JK flip flop.                                                                                                                   | 2     |  |

| d.                                                                                                                                                                                                          | What does the following gate gives the output?                                                                                                               |       |  |

|                                                                                                                                                                                                             | x yt port ?                                                                                                                                                  | 2     |  |

| e.                                                                                                                                                                                                          | What is the number of flip flops required to design mod-200 counter                                                                                          | 2     |  |

|                                                                                                                                                                                                             | II: PART - B                                                                                                                                                 | 90    |  |

|                                                                                                                                                                                                             | UNIT - I                                                                                                                                                     | 18    |  |

| 1 a.                                                                                                                                                                                                        | Express $-19$ , 750 is 2's complement representation. Then show how this number is stored at address 2000. Use hexadecimal notation to compression the data. | 9     |  |

| b.                                                                                                                                                                                                          | Design a combinational circuit whose output is 1 for the binary number > 5 and <10 and numbers from 10 - 15 are don't care condition.                        | 9     |  |

| c.                                                                                                                                                                                                          | Define universal gates. Implement the following function:                                                                                                    |       |  |

|                                                                                                                                                                                                             | i) Nand gates only<br>g = x'y + xy + xy' ii) Nor gates only iii) Nor gates only                                                                              | 9     |  |

|                                                                                                                                                                                                             | Contd?                                                                                                                                                       | 2     |  |

\_

| <b>P18</b> | IS32 Page N                                                                                      | ю 2 |

|------------|--------------------------------------------------------------------------------------------------|-----|

|            | UNIT - II                                                                                        | 18  |

| 2 a.       | Simplify the given SOP expression using Quine McCluskey method:                                  | 9   |

|            | $F(a, b, c, d) = \sum m(2, 3, 10, 11, 12, 13, 14, 15) + d(0, 1)$                                 | 9   |

| b.         | Realize the following expression using decoder:                                                  | 9   |

|            | i) $f = xy + x'y + xy'$ ii) $f = xyz + x'z + xy$ iii) $f = x'z + x'y + z'$                       | 9   |

| c.         | Implement the following using PLA                                                                |     |

|            | $f(A, B, C) = \sum m(0, 2, 4, 5, 6)$                                                             | 9   |

|            | $f(A, B, C) = \sum m(0, 1, 3, 5)$                                                                |     |

|            | UNIT - III                                                                                       | 18  |

| 3 a.       | Discuss half subtractor and Full subtractor with a neat logic circuit.                           | 9   |

| b.         | Discuss the operation of JK flip flop with truth table and design the JK flip flop circuit       | 9   |

|            | using only Nand gates.                                                                           | 7   |

| c.         | Convert the following:                                                                           | 9   |

|            | i) RS flip flop to JK flip flop ii) JK flip flop to T flip flop                                  | )   |

|            | UNIT - IV                                                                                        | 18  |

| 4 a.       | Explain the operation of 4-bit serial in serial out shift register with neat circuit diagram for | 9   |

|            | 4-bit data 1011.                                                                                 | ,   |

| b.         | Design a mod-6 counter using decade CD user and also explain the circuit diagram and             | 9   |

|            | truth table of decade counter.                                                                   | -   |

| c.         | Determine the number of possible states in a counter composed of the following number of         | 9   |

|            | flip flops: i) 8 ii) 7 iii) 9                                                                    |     |

|            | UNIT - V                                                                                         | 18  |

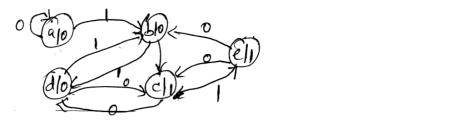

| 5 a.       | Differentiate between Moore Model and Mealy model with appropriate state transition              | 9   |

|            | diagrams.                                                                                        |     |

b. Reduce state transition diagram using row elimination method and Implication Table method.

c. How can essential Hazard to be prevented in asynchronous sequential circuits.

9

9

\* \* \*

## P18IS32