- Three processes with process ID's  $P_1$ ,  $P_2$ ,  $P_3$  with estimated completion time 6, 4, 2 milliseconds 5 a. respectively enters the ready queue together in the order P<sub>1</sub>, P<sub>2</sub>, P<sub>3</sub>. Calculate the waiting time 10 and turnaround time for each process and the average waiting time and turnaround time (Assuming there is no I/O waiting for the processes) in RR algorithm with time slice.

- b. Describe "Deadlock" situation and discuss condition favoring and different means of handling "Deadlock".

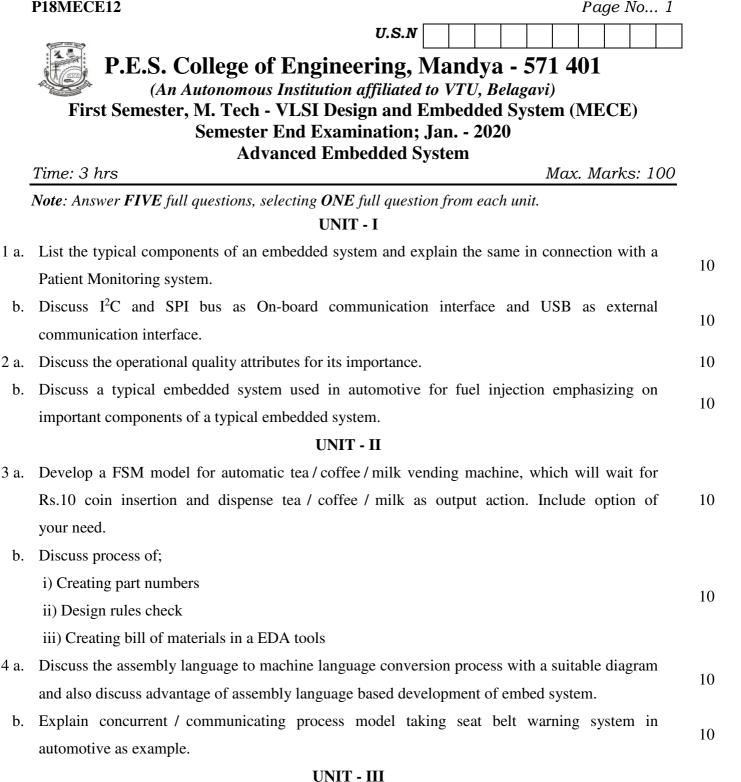

## **P18MECE12**

- 6 a. Discuss the functional and non-functional requirements in choosing the RTO's.

- b. Three processes with process ID's P<sub>1</sub>, P<sub>2</sub>, P<sub>3</sub> with estimated completion time 10, 5, 7 milliseconds respectively enters the ready queue together. A new process P<sub>4</sub> with estimated completion time 2 milliseconds enters the "Ready" queue after 2 milliseconds. Assume all the processes contain only CPU operation and no input/output operation are involved. Calculate the waiting time and turnaround time for each process and the average waiting time and turnaround time in preemptive short text job first algorithm.

## UNIT - IV

- 7 a. Discuss the following data type used in embedded C:

- i) Signed short intii) Unsigned chariii) Unsigned int10iv) Floatv) Long double

b. Write a small embedded C program to test the status of bit 5 of the status register and reset it.

If is 1, of a device, which is memory mapped to the CPU. The status register of the device is memory mapped at location 0×7000. The data bus of the controller and the status register of the device is 8 bit wide. The application should illustrate the usage of bit manipulation operations.

- 8 a. Discuss Recursion, Iteration and Reentrant functions and discuss their merits and demerits.

- b. Write a small embedded C program to complement bit 5 (assume bit numbering starts at 0) of the status register of a device which is memory mapped to the CPU. The status register of the device is memory mapped at location 0×3000. The data bus of the controller and the status register of the device is 8 bit wide.

## UNIT - V

| 9 a.  | Using Keil $\mu$ vision 3 IDE as illustrating tool explain:                       |    |

|-------|-----------------------------------------------------------------------------------|----|

|       | i) Firmware debugging operations                                                  | 10 |

|       | ii) Target flash memory programming configuration                                 |    |

| b.    | Discuss about:                                                                    |    |

|       | i) System on chip                                                                 | 10 |

|       | ii) Multi-core processors                                                         | 10 |

|       | iii) Re-configurable processors                                                   |    |

| 10 a. | Discuss following target hardware debugging techniques:                           |    |

|       | i) Magnifying glass                                                               |    |

|       | ii) Digital CRO                                                                   | 10 |

|       | iii) Logic analyzer                                                               |    |

|       | iv) Boundary scan                                                                 |    |

| b.    | List types of files generated on cross compilation and discuss any three of them. | 10 |

|       |                                                                                   |    |

10

10

10

10