P.E.S. College of Engineering, Mandya - 571 401

(An Autonomous Institution affiliated to VTU, Belagavi) Second Semester, M.Tech -Master in VLSI & Embedded System (MECE) Semester End Examination; October - 2022

## Low Power VLSI Design

| Time: 3                                                                                                              | hrs       | Max. Marks: 100   |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|-----------|-------------------|--|--|--|--|--|

| Note: I) Answer any FIVE full questions, selecting ONE full question from each unit.                                 |           |                   |  |  |  |  |  |

| <b>II</b> ) Any <b>THREE</b> units will have internal choice and remaining <b>TWO</b> unit questions are compulsory. |           |                   |  |  |  |  |  |

| III) Each unit carries 20 marks.                                                                                     |           |                   |  |  |  |  |  |

| Q. No.                                                                                                               | Questions | Marks BLs COs POs |  |  |  |  |  |

|      | UNIT - I                                                                                 | 20 |              |

|------|------------------------------------------------------------------------------------------|----|--------------|

| 1 a. | Discuss various sources of power dissipation in CMOS circuits.                           |    |              |

|      | Mention the ways to reduce old dissipation in CMOS circuits.                             | 10 | L3 CO1 PO5   |

|      | Discuss each of them with their effects.                                                 |    |              |

| b.   | With suitable equations, explain sub-threshold channel leakage                           | 7  | L2 CO1 PO5   |

|      | current of a MOS transistor.                                                             | 7  | L2 COT FOS   |

| c.   | The chip size of a CPU with in 15 mm $\times$ 25 mm clock frequency of                   |    |              |

|      | 400 MHz operating at 2.5 V. Length of the clock routing is                               |    |              |

|      | estimated to be twice the circumference of the chip. Assume that                         | 3  | L3 CO1 PO5   |

|      | the clock signal is routed on metal layer with width of 1.2 $\mu m$ and                  | 3  | Ly COT FOS   |

|      | the parasitic capacitance of the metal layer is 1 fF/ $\mu$ m <sup>2</sup> . What is the |    |              |

|      | power dissipation of the clock signal?                                                   |    |              |

|      | OR                                                                                       |    |              |

| 1 d. | Mention the steps adopted in gate-level power simulation. What is                        | 6  | L2 CO1 PO5   |

|      | the disadvantage with use of gate-level analysis?                                        |    | L2 COT FOS   |

| e.   | What are the effects of data correlation on bit switching frequency?                     | 6  | L3 CO1 PO5   |

|      | Explain them.                                                                            | 0  | LS COT FOS   |

| f.   | Explain in detail the steps used in the static statistical estimation                    | 8  | L2 CO1 PO5   |

|      | of mean.                                                                                 | 0  | L2 C01 105   |

|      | UNIT - II                                                                                | 20 |              |

| 2 a. | Explain the propagation of a static probability in logic circuits. Also                  |    |              |

|      | compute the transition density and static probability of the                             |    |              |

|      | following Boolean function, if $p(a) = 0.2$ , $p(b) = 0.3$ , $p(c) =$                    | 12 | L4 CO2 PO3,5 |

|      | 0.4, D(a) = 1, D(b) = 2  and  D(c) = 3.                                                  |    |              |

|      | y = a.b + c                                                                              |    |              |

| b.   | Derive an expression for conditional probability and frequency                           |    |              |

under memory less random signal model. Also, compute the 8 L2 CO2 PO3,5

2 d. What is transistor network restructuring? Explain. Draw the four different CMOS circuit implementation for Boolean function 10 L4 CO2 PO3,5 Y = A(B + C).e. Realize positive edge-triggered D Flip-flop and analyze its working. L3 CO2 PO3,5 6 f. Illustrate how threshold voltage can be varied by controlling the 4 L2 CO2 PO3,5 bulk bias voltage. 20 UNIT - III 3 a. Discuss with circuits, various local transformation operators for 10 L2 CO4 PO5 gate reorganization. b. Draw and explain the architecture of bus invert coding. Write the equation for expected number of transaction for regular bus and 10 L3 CO4 PO5 inverted bus. Also listed values for n = 4. OR 3 d. Draw and explain delay balance multiplier cell. List on application 7 L2 CO3 PO3,5 of it. Explain the bit line isolation used to reduce bit line swing in e. 6 L2 CO3 PO3,5 a SRAM.

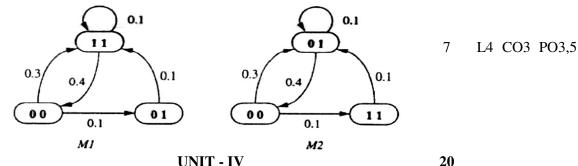

Explain transaction analysis of state and encoding. Also compute f. the expected state transaction for the following two machines.

|      |                                                                  | 20 |              |

|------|------------------------------------------------------------------|----|--------------|

| 4 a. | With the help of a block diagram explain performance management  | 8  | L2 CO4 PO5   |

|      | by voltage control.                                              | 0  | 12 004 105   |

| b.   | What is CDFG? Draw the CDFG of a system that computes            |    |              |

|      | $Y_n = a_n b_n + 5a_{n-1}$ . Use this to derive system hardware  | 6  | L4 CO4 PO5   |

|      | architecture.                                                    |    |              |

| c.   | With help of a block diagram, explain asynchronous process unit. | 6  | L2 CO4 PO5   |

|      | UNIT - V                                                         | 20 |              |

| 5 a. | Illustrate the following source of power dissipation in the DRAM |    |              |

|      | and SRAM:                                                        | 12 | L2 CO3 PO3,5 |

|      | i) Activate power sources ii) Data retention power sources       |    |              |

| b.   | Realize 16-bit carry select adder and list its operation.        | 8  | L3 CO3 PO3,5 |

|      |                                                                  |    |              |

OR